利用定制 FPGA 主板实施适用于物联网的软件定义无线电

物联网 (IoT) 包括了如此广泛的应用,但往往是一项设计就需要多个无线接口,增加了空间、功耗和成本。聪明的物联网设计师需要一种灵活的替代方式来支持多种不断发展的标准。这便是软件定义无线电 (SDR) 技术。SDR 这一理念并不新鲜;SDR 的创新之处在于解决了物联网的困境:在同一网络基础设施上融合多种射频技术的同时简化了设计、缩短了开发周期,并且降低了总体成本。本文介绍了基于定制 FPGA 主板的 SDR 设计已用于创建多协议无线数字基带解决方案。

SDR 增加了网络套接字的性能和效率

顾名思义,SDR 技术可以在同一硬件上支持多个无线协议。因实施情况而异,该技术可以同时支持这些协议,并且支持宽广(或狭窄)的频谱范围。而且,使用 FPGA 在像基站这样的无线设备中实施时,随着无线连接协议的不断发展,SDR 平台甚至可以通过重新编程来满足网络基础设施的未来需求。VotaryTech 的 SDR 平台 Arria 10AX115U3F4512SG 便是展现 SDR 潜能的范例(图 1)。这款英特尔® Arria® 10 FPGA SoC 型网卡支持广泛的无线应用,包括移动通信全球系统 (GSM)、通用分组无线业务 (GPRS)、LTE 网络宽带信号处理、跟踪和遥测。这款主板是一个前端射频平台,支持从 70 MHz 到 6 GHz 的无线应用,但其可扩展频率可高达 15 GHz。

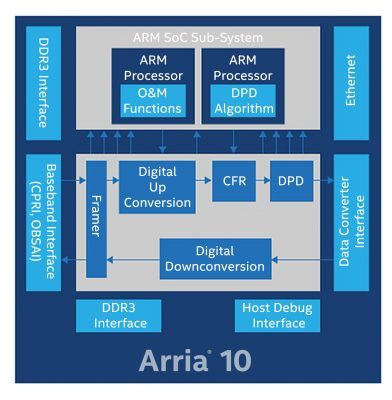

定制 10AX115U3F4512SG 支持网络应用的所有信号处理要求,包括各种调制和解调方案。主板的基带处理功能包括数字上变频、数字下变频以及标准调制器和解调器通信内核。因此,该款 SDR 平台支持无线信号收发。而且,10AX115U3F4512SG 可以在 Arria 10 FPGA 内部执行可编程和可微调基带处理。Arria 10 FPGA 可执行中频滤波和下变频等任务。

为什么在 SDR 中使用 FPGA

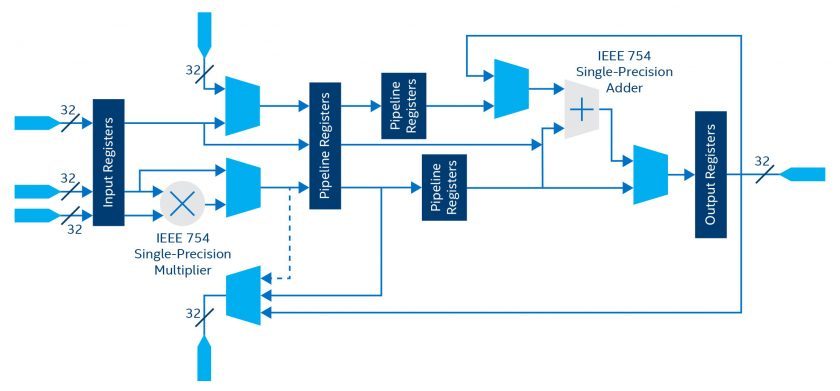

早期的 SDR 设计采用射频前端模块,深受工程师追捧,展现出了优秀的潜能。但作为一项注重应用的技术,SDR 的设计并未取得实质进展。这在某种程度上是此类系统中定制 ASIC 的要求(和成本)造成的。目前,低风险的 SoC 正在取代 SDR 平台中使用的传统 ASIC。举例来说,相比上一代高端 FPGA 而言,中档 FPGA SoC(例如采用 20 纳米工艺制造的英特尔 Arria 10)的性能提升高达 15%,功耗则下降了 60%(图 2)。而且,设备产生的热量大幅下降,这在无线设备基站、移动回程和远程无线头设计中至关重要。更为重要的是,英特尔 Arria FPGA SoC 提供了大量可变精度 DSP 模块和双核 Arm Cortex-A9 处理器选项。Arria 10 FPGA SoC 中的 DSP 模块采用三种模式:标准精度定点、高精度定点和单精度浮点(图 2)。这使得无线系统设计师能够对数字上变频和下变频及多速率滤波实施各种算法。

将这些计算功能与超过 100 万个 FPGA 逻辑元素 (LE) 和 2,400 Mbps DDR4 SDRAM 内存接口相结合,便成就了一款可编程度高的自适应平台,可以适应目前和不断涌现的无线技术(图 3)。

可合成的 IP 内核也可以集成到 FPGA 结构中,允许无线设备设计人员将模数转换器 (ADC) 输出和数模转换器 (DAC) 输入提供到 FGPA 内的基带中。这就与 I/O 和协议控制一起,在协助基于 SDR 的射频处理和基带接口方面起到了重要作用。轻松访问电路原理图以及可以使用 10AX115U3F4512SG 的 Gerber 和电路板文件简化了 SDR 功能集成。Arria 10 对于通用公共无线电接口 (CPRI) 规格的支持也提升了平台对于无线基站设计的适用性。

可编程性达到了物联网的基本要求

VotaryTech 最初开发的这项 SDR 设计是为了满足对于无线调制解调器应用的需要,但自从可以对硬件进行编程以后,也可用于遥测和波形生成模拟器等应用。Arria 10 FPGA SoC 实现的这种灵活性也使得 10AX115U3F4512SG 这类电路板十分适合物联网部署,比如由各种不断发展的技术和应用构成的物联网。但或许最重要的是,本文展示了小型设计室如何利用具有高可配置度的 FPGA SoC 设备提供适应目前和未来需求的解决方案。